IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified Vol. 5, Issue 7, July 2016

# Convolution and De-convolution using Vedic Mathematics

Ramya Annigere<sup>1</sup>, Smt. Savita S Patil<sup>2</sup>

Student, Dept of Electronics & Communication, GMIT, Davangere, India<sup>1</sup>

Assistant Professor, Dept of Electronics & Communication, GMIT, Davangere, India<sup>2</sup>

Abstract: In Digital Signal Processing, the convolution and de-convolution with a very long sequence is ubiquitous in many application areas. The basic blocks in convolution and de- convolution implementation are multiplier and divider. They consume much of time. This paper presents a direct method of computing the discrete linear convolution, circular convolution and de-convolution. The approach is easy to learn because of the similarities to computing the multiplication of two numbers. The most significant aspect of the proposed method is the development of a multiplier and divider architecture based on Ancient Indian Vedic Mathematics sutras Urdhvatriyagbhyam and Nikhilam algorithm. The results show that the implementation of linear convolution and circular convolution using vedic mathematics is efficient in terms of area and speed compared to their implementation using conventional multiplier & divider architectures. The coding is done in Verilog HDL. Simulation and Synthesis are performed using Xilinx ISE design suit 14.2. Simulated results for proposed 4x4 bit Vedic convolution circuit shows a reduction in delay of 88% than the conventional method and 41% than the OLA method.

Keywords: Linear Convolution, Circular Convolution, De-convolution, Vedic Mathematics, Urdhva Triyagbhyam, Paryavartha, VerilogHDL.

#### **I. INTRODUCTION**

ital signal processing plays a pivotal role in many 14.2. Their delays and areas are compared. Adders which areas of electrical engineering. Discrete convolution is have the highest speed and occupy a comparatively less central to many applications of Digital Signal Processing area are selected for implementing convolution. Since the and Image Processing. It is used for designing of digital execution time in most DSP algorithms mainly depends filter and cor- relation application. However, beginners upon the time required for multiplication, so there is a often struggle with convolution because the concept and computation requires a number of steps that are tedious and slow to perform. The most commonly taught approach is a graphical method because of the visual insight into the convolution mechanism. Graphical convolution is very systematic to compute but is also very tedious and time consuming [1]. The principal components required for implementation of convolution calculation are adder and multiplier for partial multiplication. Therefore the partial multiplication and addition are bottleneck in deciding the fast multiplication are Booth multiplier, array multiplier overall speed of the convolution implementation and Wallace tree multiplier [4]. Although these technique. Complexity and excess time consumption are multiplication techniques have been effective over always the major concern of engineers which motivates them to focus on more advance and simpler techniques. Pierre and John [2] have implemented a fast method for computing linear convolution, circular convolution and deconvolution. This method is similar to the multiplication of two decimal numbers and this similarity makes this method easy to learn and quick to compute. Also to compute deconvolution of two finite length sequences, a novel method is used. This method is similar to computing long-hand division and polynomial division.

As a need of proposed method, all required possible adders are studied.

With the latest advancement of VLSI technology, dig- All these adders are synthesized using Xilinx Design Suit need of high speed multiplier. Now a days, time required in multiplication process is still the dominant factor in determining the instruction cycle time of a DSP chip [3]. Traditionally shift and add algorithm is being used for designing.

> However this is not suitable for VLSI implementation and also from delay point of view. Some of the important algorithms proposed in literature for VLSI implementable conventional"shift and add" technique but their disadvantage of time consumption has not been completely removed.

> Vedic Mathematics provides unique solution for this problem. The Urdhva Triyagbhyam Sutra or vertically and Crosswise Algorithm for multiplication is discussed and then used to develop digital multiplier architecture.

> For division, different division algorithms are studied, by comparing drawbacks and advantages of each algorithm; Nikhilam Algorithm based on vedic mathematics is modified according to need and then used.

#### IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

#### II. PROPOSED ALGORITHM USING VEDIC MATHS

Vedic mathematics is an ancient Vedic mathematics which provides the unique technique of mental calculation with the help of simple rules and principles. It is based on sixteen sutras which transact different branches of mathematics i.e. algebra, geometry, arithmetic etc. In this paper the algorithms of vedic mathematics are used to design multiplier and divider. With the help of these algorithms convolution, circular convolution and deconvolution are implemented.

#### A. Convolution

In this section a novel multiplier architecture [5] based on Urdhva Triyagbhyam Sutra of Ancient Indian Vedic Mathematics is embedded into proposed method of convolution to improve its efficiency in terms of speed and area. This method for discrete convolution using vedic multiplication algorithm is best introduced by a basic example. For this example, let f(n) equal the finite length sequence (4 2 3) and g(n) equal the finite length sequence (4 5 3 4). The linear convolution of f(n) and g(n) is given by [1]:

$$y(n) = f(n) * g(n)$$

(1)

$y(n) = \sum_{k=-\infty} f(k)g(n-k)$  (2)

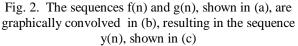

This can be solved by several methods, resulting in the sequence  $y(n) = (16\ 28\ 34\ 37\ 17\ 12)$ . This new approach for calculating the convolution sum is set up like multiplication where the convolution of f(n) and g(n) is performed as follows:

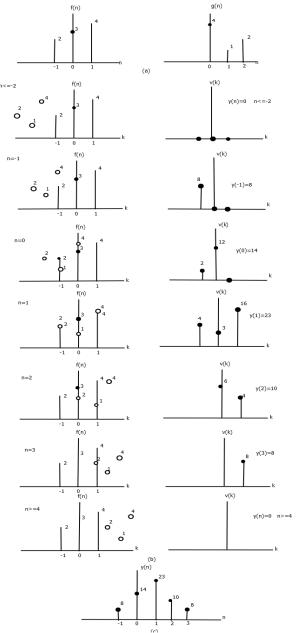

As seen in the Fig. 2 computation of the convolution sum, the approach is similar to multiplication calculation, except carries are not performed out of a column. This first example shows the simplicity of this method and how easily the calculation can be performed. As shown below, this method can be used to check intermediate values in graphical convolution, as well as the final answer. In Fig. 1, the convolution sum is computed using graphical convolution. Fig. 1(a) shows the sequences f(n) and g(n). For each value of n, the convolution sum consists of a folding, translation, multiplication, and summation. For a given value of n, the summation is a product of the sequence f(k) and the folded and translated sequence g(nk). The left-hand column of Fig. 1(b) shows both sequences f(k) and g(n-k) for each value of n, and the right-hand column shows the product of the two sequences

$$v_n(k)$$

which is given by

$v_n(k) = f(k)g(n-k)$  (3)

Vedic mathematics is an ancient Vedic mathematics which The value of the convolution sum for each value of n is

$$f(n) * g(n) = v_n(k)$$

(4)

k

The final answer for the graphical convolution method is shown in Fig. 1(c). This answer was verified above using the new method. The sequence  $v_n(k)$ , which is an intermediate an- swer in computing the convolution sum, may also be checked as shown below using the method presented in this paper.

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

| g(n):<br>f(n):           |    | *        |    | 1<br>3   | -  | k            |

|--------------------------|----|----------|----|----------|----|--------------|

| v(1):<br>v(0):<br>v(-1): | 08 | 12<br>02 | 03 | 04<br>06 | 08 | 1<br>0<br>-1 |

| y(n):                    | 08 | 14       | 23 | 10       | 08 | •            |

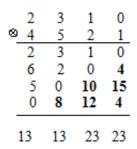

r: -1 0 1 2 3 Fig. 3. Verification of intermediate terms using proposed method

Above example illustrates the ease in computing the convolution sum for finite sequences using this new method.

1) Vedic Mutiplier:Urdhva Triyagbhyam: Among all avail- able multipliers, this paper proposes a systematic design methodology for fast and area efficient digit multiplier based on Vedic Mathematics. In the proposed convolution method the multiplier architecture is based on an algorithm Urdhva Triyagbhyam (Vertical and Crosswise) of Ancient Indian Vedic Mathematics [5].

The use of Vedic Mathematics lies in the fact that it reduces the typical calculations in conventional mathematics to very simple ones. Urdhva Tiryagbhyam Sutra is a general multiplication formula applicable to all cases of multiplication [6]. Because of parallelism in generation of partial products and their summation obtained, speed is improved. In this algorithm the small block can be wisely utilized for design- ing bigger NxN multiplier. For higher no. of bits in input, little modification is required. Divide the no. of bit in the inputs equally in two parts. Let's analyse 4x4 multiplications, say A3A2A1A0 and B3B2B1B0. Following are the output line for the multiplication result, S7S6S5S4S3S2S1S0. Let's divide A and B into two parts, say A3A2&A1A0 for A and B3B2&B1B0 for B. Using the fundamental of Vedic multi- plication, taking two bit at a time and using 2 bit multiplier block, we can have the following structure for multiplication below.

| A3 A2           | A3 A2           | A1 A0           | A1 A0           |

|-----------------|-----------------|-----------------|-----------------|

| B3 B2           | B1 B0           | B3 B2           | B1 B0           |

| S33 S32 S31 S30 | S23 S22 S21 S20 | S13 S12 S11 S10 | S03 S02 S01 S00 |

Assuming the output of each multiplication is as given above. For the final result, add the middle product term along with the term shown below.

| \$33\$32                                                        | S31 S30 0 | 0 |

|-----------------------------------------------------------------|-----------|---|

| S01S00 S23 S22 S21 S20                                          |           |   |

| S <sub>13</sub> S <sub>12</sub> S <sub>11</sub> S <sub>10</sub> |           |   |

| 0 0 S03 S02                                                     |           |   |

The first two outputs S0 and S1 are same as that of circular translation in circular convolution. The far left S00 and S01. Result of addition of the middle terms by value in the circular convolution solution corresponds to using two, 4 bit full adders will forms output line from y(N-1) where N is the length of the sequence.

S5S4S3S2. One of the full adder will be used to add (S23S22S21S20) and (S13S12S11S10) and then the second full adder is required to add the result of  $1^{\text{st}}$  full adder with (S31S30S03S02). The respective sum bit of the  $2^{\text{nd}}$  full adder will be S5S4S3S2. Now the carry generated during  $1^{\text{st}}$  full adder operation and that during  $2^{\text{nd}}$  full adder operation should be added using half adder so that the final carry and sum to be added with next stage i.e. with S33S32 to get S7S6. The same can be extended for input bits 8, 16, 32.

#### B. Circular Convolution

Circular convolution has many applications and is usually introduced to electrical engineering students in a digital signal processing. The novel method for computing linear convolution using vedic mathematics from above subsection is easily modified for circular convolution [2]. This method of computing circular convolution is best illustrated by example. Let  $f(n) = (2 \ 3 \ 1 \ 0)$  and  $g(n) = (4 \ 5 \ 2 \ 1)$ . The circular convolution of f(n) and g(n) is given by

$$y(n) = f(n) * g(n)$$

(5)

$$y(n) = \int_{k=0}^{\infty} f(k)g((n-k)modN)$$

(6)

Fig. 4 Block diagram presentation for 4x4 multiplications

Each block as shown above is 2x2 multiplier. First 2x2 multiplier inputs are A1A0 and B1B0. The last block is 2x2 multiplier with inputs A3A2 and B3B2. The middle one shows two, 2x2 multiplier with inputs A3A2 and B1B0 and A1A0 and B3B2. So the final result of multiplication, which is of 8 bit, S7S6S5S4S3S2S1S0, can be interpreted as given  $y(n)=(13\ 13\ 23\ 23)$  where N is the length of the sequences. This circular convolution calculation may be performed similar to the method for linear convolution from above subsection. The multiplier architecture is implemented using vedic algo- rithm.

The location of the triangle of bold faced numbers is repositioned for circular convolution compared with linear convolution. The location of these numbers is due to the circular translation in circular convolution. The far left value in the circular convolution solution corresponds to y(N - 1) where N is the length of the sequence.

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

#### y(3) y(2) y(1) y(0)

Fig5 Circular Convolution by proposed method

#### C. Deconvolution

A direct method is also presented for the deconvolution of two finite length discrete-time sequences. This deconvolution method is similar to computing long-hand division and polyno- mial division, just as the direct convolution method is similar to multiplication [7]. Many TABLE I.DEVICE UTILIZATION SUMMARY FOR other deconvolution methods are available. In this section, a basic recursive deconvolution method for finite length sequences is computed. This recursion can be carried out in a manner similar to long division.

Fig. 6. De-convolution by proposed method

Division operation is implemented by using Nikhilam algorithm based on vedic mathematics while to obtain partial products vedic multiplier is used. For instance, the first exam- ple in subsection A may be reworked, solving for f(n) given g(n) and y(n). The sequences are set up in a fashion similar to long division, as shown in Fig. 6, but where no carries are performed out of a column.

1) Vedic Divider: The Paravartya sutra, the digits of the divisor is complimented other than the most significant bit, this complemented digit is initially multiplied with the most significant digit of the dividend and this multiplication result is added with columns of dividend. The result of addition is again multiplied with complemented digits of Divisor and added with the remaining column of the dividend, trailed consecutive multiplication and totalling of successive column. The summary of all columns outcomes procedures proportion and balance.

The algorithm is demonstrated below Assuming the dividend is 14589 and divisor is 132. The division of this two numbers using Paravartya sutra is shown in fig.7

|   | Divisor |    | Dividend       |           |         |         |   |

|---|---------|----|----------------|-----------|---------|---------|---|

| 1 | 3       | 2  | 1              | 1 4 5 8 9 |         |         |   |

|   | -3      | -2 |                | -3        | -2      |         |   |

|   |         |    |                |           | -3      | -2      |   |

|   |         |    |                |           |         | 0       | 0 |

|   |         |    | 1              | 1         | 0       | 6       | 9 |

|   |         |    | Quotient = 110 |           | Reminde | er = 69 |   |

Fig.7 Division using Paravartya sutra

#### **III. SIMULATIONS AND RESULTS**

The vedic convolution algorithm proposed in this paper is simulated and synthesized using the Xilinx Design Suit 14.2 with the device family as Spartan3 and device XC3S400- 5fg320. The table 1 below shows the synthesis report of the proposed work for convolution using vedic maths with the logic resource utilization.

## CONVOLUTION

| Logic Utilization | Used | Available | Utilization |

|-------------------|------|-----------|-------------|

| No. of Slices     | 358  | 3584      | 9%          |

| No. of LUTs       | 623  | 7168      | 8%          |

| No. of Bounded    | 96   | 221       | 48%         |

The simulated results of convolution and circular convolution are shown below:

|                |       |     | t            |

|----------------|-------|-----|--------------|

| Name           | Value |     | 1,000,001 ps |

| 🕨 📑 a[3:0]     | 4     | 15  | 4            |

| 🕨 📑 b[3:0]     | 5     | 14  | 5            |

| 🕨 📑 c[3:0]     | 3     | 12  | 3            |

| 🕨 📑 d[3:0]     | 4     | 13  | 4            |

| 🕨 📑 e[3:0]     | 0     | 10  | 0            |

| 🕨 📑 f[3:0]     | 2     | 11  | 2            |

| 🕨 📑 g[3:0]     | 6     | 9   | 6            |

| 🕨 📑 h[3:0]     | 3     | 8   | 3            |

| ▶ 📑 conv0[7:0] | 12    | 104 | 12           |

| ▶ 📑 conv1[8:0] | 33    | 213 | 33           |

| ▶ 📑 conv2[9:0] | 41    | 363 | 41           |

| ▶ 📑 conv3[9:0] | 48    | 508 | 48           |

| 🕨 📑 conv4[9:0] | 34    | 409 | 34           |

| ▶ 📑 conv5[8:0] | 8     | 305 | 8            |

| 🕨 📑 conv6[7:0] | 0     | 150 | <u> </u>     |

Fig 8 Simulation results of Convolution using Vedic **Mathematics**

| Name            | Value         | 2,000,000 ps   | 2,000,001 ps |

|-----------------|---------------|----------------|--------------|

| 🕨 📑 a[3:0]      | 4             | 15             | X 4          |

| 🕨 📑 b[3:0]      | 5             | 14             | 5            |

| 🕨 📑 c[3:0]      | 3             | 12             | 3            |

| 🕨 📑 d[3:0]      | 4             | 13             | 4            |

| 🕨 📷 e[3:0]      | 0             | 10             | × •          |

| 🕨 📑 f[3:0]      | 2             | 11             | 2            |

| 🕨 📑 g[3:0]      | 6             | 9              | <b>x</b> 6   |

| 🕨 📑 h[3:0]      | 3             | 8              | X 3          |

| 🕨 📷 conv0[9:0]  | 46            | 513            | 46           |

| 🕨 📷 conv1[9:0]  | 41            | 518            | 41           |

| 🕨 📷 conv2[9:0]  | 41            | 513            | 41           |

| 🕨 📷 conv3[9:0]  | 48            | 508            | 48           |

| Fig 0 Simulatio | n maguilta of | Cincular Conv. | alution wain |

Fig 9 Simulation results of Circular Convolution using **Vedic Mathematics**

### **IJARCCE**

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

| Table II: Execution Times for Conventional Method |

|---------------------------------------------------|

| Using Vedic Maths and Proposed Method             |

| Input Sequence Length   | 216       | 220      |

|-------------------------|-----------|----------|

| Conventional Method [7] | 195.059ns |          |

| Proposed Vedic Method   | 21.661ns  | 22.943ns |

Tables 2 shows delay improvement of proposed circuit of<br/>convolution over the circuit implemented using [4]<br/>conventional array multiplier and overlap & add method<br/>for different input sequence length. From the table it is<br/>clear that proposed method provides 41% delay [5]<br/>improvement than OLA method and 88% improvement<br/>than Conventional method. Table 3 shows comparison of<br/>delay for vedic circular convolution over the conventional<br/>[6]

#### Table III: Comparision of For Vedic Circular Convolution over the Conventional Circular Convolution

| Method                            | Delay    |

|-----------------------------------|----------|

| Conventional Method(inbuilt) [10] | 62.47us  |

| Proposed Vedic Method             | 21.963ns |

|                               | Messages |          |             |            |

|-------------------------------|----------|----------|-------------|------------|

| +                             |          | 16       | 16          |            |

|                               |          | 28       | 28          |            |

|                               |          | 34       | 34          |            |

| De_Convalution_Main/Conv_Out3 |          | 37       | 37          |            |

|                               |          | 17       | 17          |            |

|                               |          | 12       | 12          |            |

|                               |          | 4        | 4           |            |

|                               |          | 5        | 5           |            |

| =/De_Convalution_Main/g2      |          | 3        | 3           |            |

|                               |          | 4        | 4           |            |

| + 🔷 /De_Convalution_Main/Out  |          | 423      | 423         |            |

| De_Convalution_Main/W1        |          | 00010100 | 00010100    |            |

|                               |          | 00001100 | 00001100    |            |

|                               |          | 00010000 | 00010000    |            |

|                               |          | 00001010 | 00001010    |            |

|                               |          | 00000110 | 00000110    |            |

|                               |          | 00001000 | 00001000    |            |

|                               |          | 00001111 | 00001111    |            |

|                               |          | 00001001 | 00001001    |            |

|                               |          | 00001100 | 00001100    |            |

|                               |          | 00000100 | 00000100    |            |

|                               |          | 00000010 | 00000010    |            |

|                               |          | 00000011 | 00000011    |            |

|                               | Now      | 600 ps   | ) ps 400 ps | 500 ps 600 |

| 2 <del>-</del>                | Cursor 1 | 472 ps   | 472         |            |

Fig.10. Simulation results of De-convolution

#### **IV. CONCLUSION**

The main focus of this paper is to introduce a method for calculating the linear convolution, circular convolution and deconvolution with the help of vedic algorithms that is easy to learn and perform. The execution time and area of the proposed method for convolution using vedic multiplication algorithm is compared with that of convolution with the simple multiplication is less. From the simulated results it is observed that delay of Linear Convolution architecture is reduced by approximately 88% than the conventional method. An extension of the proposed linear convolution approach to circular convolution using vedic multiplier is also introduced which has less delay and area than the conventional method. This paper also introduces a straightforward approach to performing the de-convolution.

#### REFERENCES

- J. G. Proakis and D. G. Manolakis, "Digital Signal Processing: Principles, Algorithm, and Applications," 2nd Edition. New York Macmillan, 1992.

- [2] Pierre, John W. "A novel method for calculating the convolution sum of two finite length sequences." Education, IEEE Transactions on 39.1(1996):77-80

- [3] Rudagi, J. M., Vishwanath Ambli, Vishwanath Munavalli, Ravindra Patil, and Vinaykumar Sajjan. "Design and implementation of efficient multiplier using Vedic mathematics." (2011): 162-166.

- [4] Vaidya, Sumit, and Deepak Dandekar. "Delay-Power Performance Comparison of multipliers in VLSI circuit design." International Journal of Computer Networks & Communications (IJCNC) 2.4 (2010): 47-56.

- [5] Akhter, Shamim. "VHDL implementation of fast NxN multiplier based on vedic mathematic." In Circuit Theory and Design, 2007. ECCTD 2007. 18th European Conference on, pp. 472-475. IEEE, 2007.

- [6] Thapliyal, Himanshu, and M. B. Srinivas. "High Speed Efficient NxN Bit Parallel Hierarchical Overlay Multiplier Architecture Based on Ancient Indian Vedic Mathematics." Enformatika Trans 2 (2004): 225-228.

- [7] Lomte, Rashmi K., and P. C. Bhaskar. "High Speed Convolution and Deconvolution Using Urdhva Triyagbhyam." VLSI (ISVLSI), 2011 IEEE Computer Society Annual Symposium on. IEEE, 2011.

- [8] Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaja, "Vedic Mathematics." Motilal Banarsidass, New Delhi, India, 1994.

- [9] Hanumantharaju, M. C., et al."A High Speed Block Convolution using Ancient Indian Vedic Mathematics." Conference on Computational Intelligence and Multimedia Applications, 2007. International Conference on. Vol. 2. IEEE, 2007.

- [10] Itawadiya, Akhalesh K., et al. "Design a DSP operations using vedic mathematics." Communications and Signal Processing (ICCSP), 2013 International Conference on. IEEE, 2013

#### **BIOGRAPHIES**

**Ramya Annigere** received the BE degree in Electronics & Instrumentation from Kuvempu University at University BDT College of Engineering, Davangere. She is currently pursuing M.Tech in Digital Electronics from Visvesvarya Technological University at

GM Institute of Technology, Davangere.

**Savita S Patil** received the M.Tech degree in VLSI. She is currently working as Assistant Professor in Department of Electronics and Communication at GM Institute of Technology, Davangere.